Freedom CPU Project

#### F-CPU Design Team

Draft and Request For Comment

## F-CPU MANUAL REV. 0.2.5

"Design and let design"

Please visit us at http://www.f-cpu.org and send comments to the F-CPU mailing list at f-cpu@seul.org.

#### 0.1 Copyright and distribution licence:

This manual is distributed under the terms of the GFDL, or "GNU Free Documentation License", which text can be found on the GNU web site (http://www.gnu.org). A copy of this licence is included in this package (fdl.htm).

Copyright (c) 1999-2002 The F-CPU Group Design Team.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

#### 0.2 Foreword:

Although the overall specifications are getting slowly more stable, everything in this document is *furiously* preliminary and changes often without notice. Please keep in touch with the group on the mailing list and check the latest updates on the official F-CPU web site.

This document is (C) 1999-2002 The F-CPU Group Design Team and is a *work of collaboration*. Anybody can participate to the F-CPU effort and become a team member by subscribing to the mailing lists and taking part to the discussions. You are welcome to submit your ideas and report errors. We are conscious that this document always contains errors but we are working on (or around?) them constantly.

This manual has been translated to several file formats and may additionally lack some parts or contain some errors. It is very incomplete even though it's becoming huge!

#### 0.3 Revision history:

- o Created July 8, 1999 by Whygee@f-cpu.org (Yann Guidon) with extracts from Mathias Brossard's RFC

- o July 10: added some more.

- o 11th: adapted for converstion to PDF with HTMLDOC.

- o 8/2, 8/8, 8/9, 8/13: added yet some more.

- o 8/25: reworked a bit (what-why, TTA, endianness, paging, jump station...)

- o 11/5: merged with some other non-architectural contents.

- o 11/16: revamped it all for HTML back.

- o 2/27: major revision of the instruction encoding. Imm6 disappears and most of the old errors/mistypings are corrected.

- o 3/15: Adapted the CPP macro processing (at last)

- o 12/18/2000: Olivier Jean finally published his Latex version of manual

- o 12/24/2000 : YG patches. very incomplete!

- o 12/30/2000: YG patches again in Berlin.

- o 1/\*/2001: beginning of a french translation, redrawing of the illustrations, major update....

- o 02/05/2002: starting new organisation of the manual (Cedric BAIL, bail\_c@epita.fr).

- o 04/19/2002: updating the manual with Michael RIEPE recommandation.

- o 04/30/2002: adding index.

A lot of comments are also given by other people, sometimes anonymouns, on the mailing lists.

#### 0.4 Missing:

- \* alphabetic-ordered instruction set map

- \* instruction set table, sorted by hex. opcode value

- \* more examples in the instruction descriptions

- \* IRQ/traps

- \* SR map

- \* parts 8 and 9

- \* and a lot of other stuffs !!!

#### 0.5 Hyperlink jump station:

#### HTTP:

- \* The F-CPU main sites: http://www.f-cpu.org and http://www.f-cpu.de

- \* The latest update of the F-CPU Manual: http://www.f-cpu.seul.org

- \* The latest CVS-Snapshots at: http://f-cpu.gaos.org

#### The mailing lists:

- \* http://www.seul.org/archives/f-cpu/f-cpu (main list)

- \* http://lists.april.org/wws/info/f-cpu\_france (french list)

- \* http://www.eGroups.com/list/fcpu-ger (german list, outdated)

Mailing lists ar

## Contents

|    | 0.1<br>0.2<br>0.3<br>0.4<br>0.5                       | Copyright and distribution licence:                                                                                                                                                                                                                                                                                                                                                        | 2<br>2<br>2<br>3<br>3                              |

|----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Ι  | $\mathbf{Th}$                                         | e F-CPU Project, description and philosophy                                                                                                                                                                                                                                                                                                                                                | 11                                                 |

| 1  | Desc                                                  | cription of the F-CPU project                                                                                                                                                                                                                                                                                                                                                              | 12                                                 |

| 2  | Freq<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Introduction                                                                                                                                                                                                                                                                                                                                                                               | 14<br>14<br>16<br>16<br>17<br>17                   |

| 3  | The 3.1                                               | genesis of the F-CPU Project  The Freedom CPU Architecture: A GNU/GPL'ed high-performance 64-bit microprocessor developed in an open, Web-wide collaborative environment.  3.1.1 History  3.1.2 The Freedom GNU/GPL'ed architecture  3.1.3 Developing the Freedom architecture: issues and challenges  3.1.4 Tools  3.1.5 Conclusion  3.1.6 Appendix A  3.1.7 Appendix B  3.1.8 Appendix C | 19<br>19<br>20<br>20<br>21<br>21<br>22<br>23<br>24 |

| 4  | A bi 4.1 4.2 4.3                                      | it of F-CPU history           M2M                                                                                                                                                                                                                                                                                                                                                          | 25<br>25<br>25<br>28                               |

| 5  | The                                                   | design constraints                                                                                                                                                                                                                                                                                                                                                                         | 29                                                 |

| 6  | The                                                   | project's roadmap                                                                                                                                                                                                                                                                                                                                                                          | 31                                                 |

| II | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8  | eneral description of the F-CPU  The main characteristics                                                                                                                                                                                                                                                                                                                                  | 33<br>34<br>34<br>35<br>36<br>38<br>38             |

|    | 2.9                                                   | The F-CPU has no stack pointer                                                                                                                                                                                                                                                                                                                                                             | 39                                                 |

|                       | 2.10 The F-CPU has no condition code register                                                                                                                                                                                                                                                                              | 39<br>39<br>40<br>40<br>41<br>41                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| ΙΙ                    | I General description of the F-CPU Core #0                                                                                                                                                                                                                                                                                 | 43                                                 |

| 1                     | About the FC0 core  1.1 The FC0 is superpipelined                                                                                                                                                                                                                                                                          | 44<br>44<br>45<br>46                               |

| 2                     | Evolution of the FC0                                                                                                                                                                                                                                                                                                       | 47                                                 |

| 3                     | The FC0 Execution Units 3.1 The "logic" unit (ROP2) 3.2 The "bit scrambling" unit () 3.3 The "increment" unit 3.4 The add/sub unit 3.5 The integer multiply unit 3.6 The integer divide unit 3.7 The Load/Store unit 3.8 Population count / Single Error Correction (POPC) 3.9 Other units 3.10 Extensions and scalability | 51<br>53<br>54<br>55<br>56<br>56<br>56<br>56<br>56 |

|                       |                                                                                                                                                                                                                                                                                                                            |                                                    |

| I                     | V Advanced topics                                                                                                                                                                                                                                                                                                          | <b>58</b>                                          |

| I\<br>1               | V Advanced topics  The exceptions                                                                                                                                                                                                                                                                                          | 58<br>60                                           |

|                       | •                                                                                                                                                                                                                                                                                                                          |                                                    |

| 1                     | The exceptions                                                                                                                                                                                                                                                                                                             | 60                                                 |

| 1<br>2                | The exceptions  The Smooth Register backup mechanism                                                                                                                                                                                                                                                                       | 60<br>62                                           |

| 1<br>2<br>3           | The exceptions The Smooth Register backup mechanism The scheduler                                                                                                                                                                                                                                                          | 60<br>62<br>65                                     |

| 1<br>2<br>3<br>4      | The exceptions  The Smooth Register backup mechanism  The scheduler  The memory units (Fetcher and L/SU)                                                                                                                                                                                                                   | 60<br>62<br>65<br>67                               |

| 1<br>2<br>3<br>4<br>V | The exceptions  The Smooth Register backup mechanism  The scheduler  The memory units (Fetcher and L/SU)  The F-CPU Instruction Set Architecture                                                                                                                                                                           | 60<br>62<br>65<br>67                               |

| 1 2 3 4 V 1           | The exceptions The Smooth Register backup mechanism The scheduler The memory units (Fetcher and L/SU)  The F-CPU Instruction Set Architecture Designing an instruction set                                                                                                                                                 | 60<br>62<br>65<br>67<br>68<br>69                   |

| 1 2 3 4 V 1 2         | The exceptions The Smooth Register backup mechanism The scheduler The memory units (Fetcher and L/SU)  The F-CPU Instruction Set Architecture Designing an instruction set Instruction formats                                                                                                                             | 60<br>62<br>65<br>67<br>68<br>69<br>71             |

| $\mathbf{V}$ | I ] | F-CPU         | J Instruction Set draft                  | 77                |

|--------------|-----|---------------|------------------------------------------|-------------------|

| 1            | Ari |               | c Operations                             | 78                |

|              | 1.1 | Core A        | Arithmetic operations                    | 78                |

|              |     | 1.1.1         | add                                      | 78                |

|              |     | 1.1.2         | sub                                      | 80                |

|              |     | 1.1.3         | mul                                      | 82                |

|              |     | 1.1.4         | div                                      | 84                |

|              | 1.2 |               | al Arithmetic operations                 | 86                |

|              | 1.2 | 1.2.1         | •                                        | 86                |

|              |     | 1.2.1 $1.2.2$ |                                          |                   |

|              |     |               | subi                                     | 87                |

|              |     | 1.2.3         | muli                                     | 88                |

|              |     | 1.2.4         | divi                                     | 89                |

|              |     | 1.2.5         | mod                                      | 90                |

|              |     | 1.2.6         | modi                                     | 91                |

|              |     | 1.2.7         | mac                                      | 92                |

|              |     | 1.2.8         | addsub                                   | 94                |

|              |     | 1.2.9         | popcount                                 | 95                |

|              |     | 1.2.10        | popcounti                                | 96                |

|              | 1.3 |               | nal increment-based operations           | 97                |

|              |     | 1.3.1         | inc                                      | 97                |

|              |     | 1.3.2         | dec                                      | 98                |

|              |     | 1.3.2 $1.3.3$ | neg                                      | 99                |

|              |     | 1.3.4         |                                          | 100               |

|              |     |               | scan                                     |                   |

|              |     | 1.3.5         | cmpl                                     | 102               |

|              |     | 1.3.6         | cmple                                    | 103               |

|              |     | 1.3.7         | cmpli                                    | 104               |

|              |     | 1.3.8         | cmplei                                   | 105               |

|              |     | 1.3.9         | abs                                      | 106               |

|              |     | 1.3.10        | max                                      | 107               |

|              |     | 1.3.11        | min                                      | 108               |

|              |     | 1.3.12        | maxi                                     | 109               |

|              |     |               | mini                                     | 110               |

|              |     |               | sort                                     | 111               |

|              | 1.4 |               | nal Logarithmic Number System operations | 112               |

|              | 1.1 | 1.4.1         | ladd                                     |                   |

|              |     | 1.4.2         | lsub                                     |                   |

|              |     |               |                                          |                   |

|              |     | 1.4.3         | l2int                                    |                   |

|              |     | 1.4.4         | int2l                                    | 115               |

| 2            | D:4 | C1            |                                          | 110               |

| 2            |     |               | ng based operations                      | 116               |

|              | 2.1 |               | Shift and Rotate operations              | 116               |

|              |     | 2.1.1         | shift                                    | 116               |

|              |     | 2.1.2         | shiftr                                   | 117               |

|              |     | 2.1.3         | shiftra                                  | 118               |

|              |     | 2.1.4         | rotl                                     | 119               |

|              |     | 2.1.5         | rotr                                     | 120               |

|              | 2.2 | Option        | nal Shift and Rotate operations          | 121               |

|              |     | 2.2.1         | shiftli                                  | 121               |

|              |     | 2.2.2         | shiftri                                  | 122               |

|              |     | 2.2.3         | shiftrai                                 | 123               |

|              |     | 2.2.4         | rotli                                    | 124               |

|              |     | 2.2.4 $2.2.5$ | rotri                                    | $\frac{124}{125}$ |

|              |     |               |                                          | _                 |

|              |     | 2.2.6         | bitop                                    | 126               |

|              | 0.0 | 2.2.7         | bitopi                                   | 127               |

|              | 2.3 | -             | nal Bit Shuffling operations             | 128               |

|              |     | 2.3.1         | bitrev                                   | 128               |

|              |     | 2.3.2         | bitrevi                                  | 130               |

|              |     | 2.3.3         | byterev                                  | 131               |

|              |     | 2.3.4         | mix                                      | 132               |

|              |     | 2.3.5         | expand                                   | 134               |

|              |     | 2.3.6         | sdup                                     | 136               |

| 3 | Log      | c operations 137                                                                       |

|---|----------|----------------------------------------------------------------------------------------|

|   | 3.1      | Core Logic operations                                                                  |

|   |          | 3.1.1 logic                                                                            |

|   | 3.2      | Optional Logic operations                                                              |

|   |          | 3.2.1 logici                                                                           |

|   |          |                                                                                        |

| 4 | Floa     | ting Point Operations 140                                                              |

|   | 4.1      | Level 1 Floating Point Operations                                                      |

|   |          | 4.1.1 fadd                                                                             |

|   |          | 4.1.2 fsub                                                                             |

|   |          | 4.1.3 fmul                                                                             |

|   |          | 4.1.4 f2int                                                                            |

|   |          |                                                                                        |

|   |          | $4.1.5  \text{int2f}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|   |          | 4.1.6 fiaprx                                                                           |

|   |          | 4.1.7 fsqrtiaprx                                                                       |

|   |          | 4.1.8 fcmple                                                                           |

|   |          | 4.1.9 fcmpl                                                                            |

|   | 4.2      | Level 2 Floating Point Operations                                                      |

|   |          | 4.2.1 fdiv                                                                             |

|   |          | 4.2.2 fsqrt                                                                            |

|   | 4.3      | Level 3 Floating Point Operations                                                      |

|   | -        | 4.3.1 flog                                                                             |

|   |          | 4.3.2 fexp                                                                             |

|   |          | 4.3.3 fmac                                                                             |

|   |          | 4.3.4 faddsub                                                                          |

|   |          | 4.5.4 laddsub                                                                          |

| 5 | Mor      | nory Access operations 156                                                             |

| J | 5.1      | Core Memory Access operations                                                          |

|   | 5.1      | · -                                                                                    |

|   |          |                                                                                        |

|   |          | 5.1.2 store                                                                            |

|   | 5.2      | Optional Memory Access operations                                                      |

|   |          | 5.2.1 load                                                                             |

|   |          | 5.2.2 store                                                                            |

|   |          | 5.2.3 loadi                                                                            |

|   |          | 5.2.4 storei                                                                           |

|   |          | 5.2.5 loadf, storef, loadif, storeif                                                   |

|   |          | 5.2.6 cachemm                                                                          |

|   |          |                                                                                        |

| 6 | Dat      | a move operations 168                                                                  |

|   | 6.1      | Core Data move operations                                                              |

|   |          | 6.1.1 move                                                                             |

|   |          | 6.1.2 loadcons                                                                         |

|   |          | 6.1.3 loadconsx                                                                        |

|   |          | 6.1.4 get                                                                              |

|   |          | 6.1.5 put                                                                              |

|   | 6.2      | Optional Data move operations                                                          |

|   | 0.2      |                                                                                        |

|   |          |                                                                                        |

|   |          | 6.2.2 storem                                                                           |

|   |          | 6.2.3 geti                                                                             |

|   |          | 6.2.4 puti                                                                             |

| _ | <b>.</b> |                                                                                        |

| 7 |          | ruction Flow Control instructions 180                                                  |

|   | 7.1      | Core Instruction Flow Control instructions                                             |

|   |          | 7.1.1 jmpa                                                                             |

|   |          | 7.1.2 loadaddr                                                                         |

|   |          | 7.1.3 loadaddri                                                                        |

|   |          | 7.1.4 loopentry                                                                        |

|   |          | 7.1.5 loop                                                                             |

|   |          | 7.1.6 syscall                                                                          |

|   |          | 7.1.7 halt                                                                             |

|   |          | 7.1.8 rfe                                                                              |

|   | 7.2      | Optional Instruction Flow Control instructions                                         |

|   | 1.4      | Optional manucion flow Control manuciona                                               |

|              |     | 7.2.1<br>7.2.2<br>7.2.3 | srb_save          | <br> |  | <br> | . 1 | 90         |

|--------------|-----|-------------------------|-------------------|------|--|------|-----|------------|

| V            | II  | Progr                   | ramming the F-CPU |      |  |      | 19  | <b>}</b> 2 |

| 1            | Int | roducti                 | ion               |      |  |      | 19  | 93         |

| 2            | cal | l conve                 | ention            |      |  |      | 19  | 94         |

| 3            | Pse | eudo-su                 | uperscalar        |      |  |      | 19  | 95         |

| $\mathbf{V}$ | III | Inde                    | ex                |      |  |      | 19  | 97         |

## List of Figures

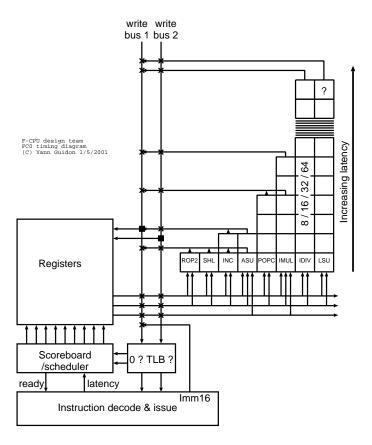

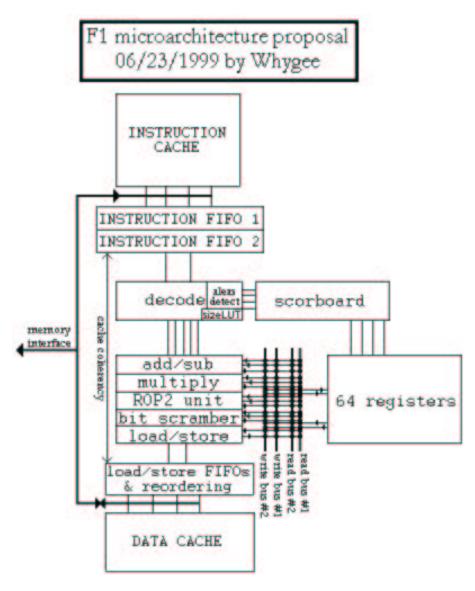

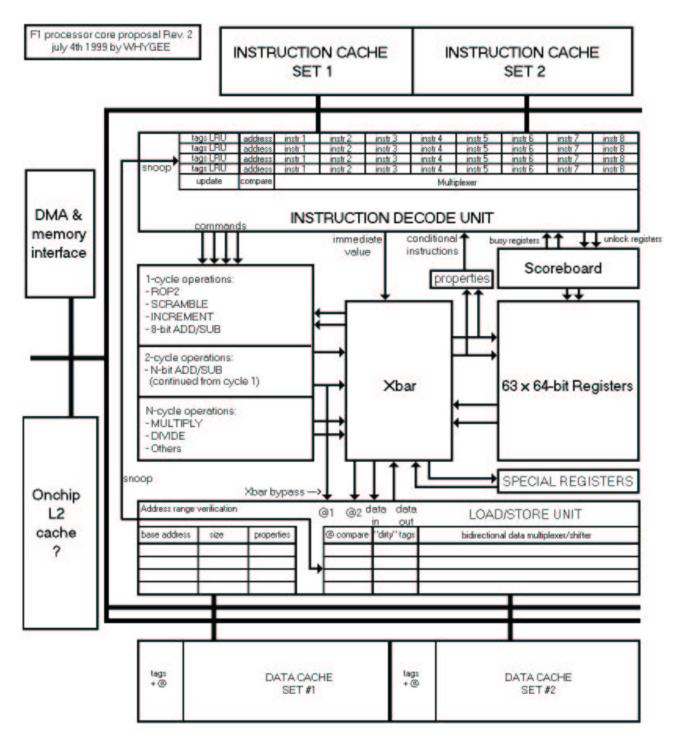

| 1.1 | The pipeline is folded around the Xbar                                            |

|-----|-----------------------------------------------------------------------------------|

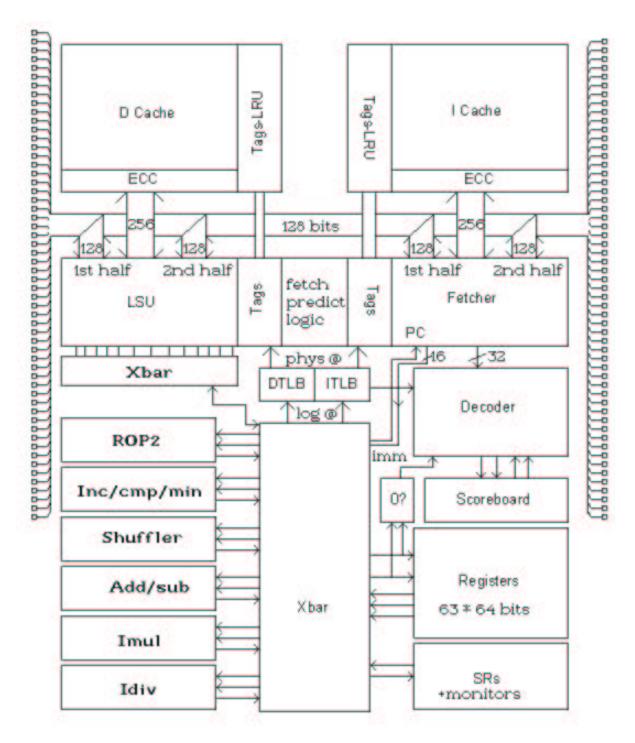

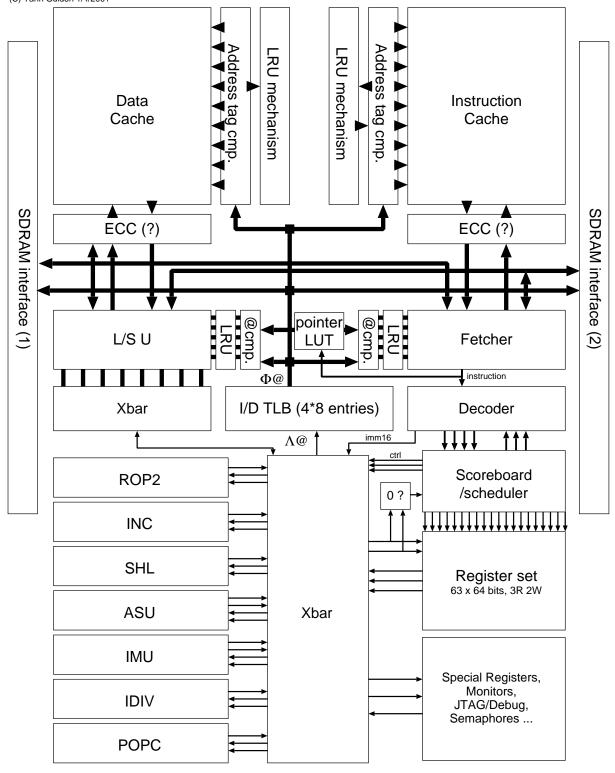

| 2.1 | The first F-CPU chip proposal                                                     |

| 2.2 | A more precise, first-attempt F-CPU description                                   |

| 2.3 | A third F-CPU description                                                         |

| 2.4 | The current F-CPU diagram                                                         |

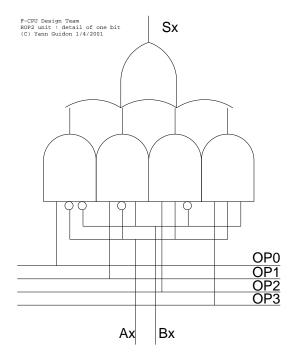

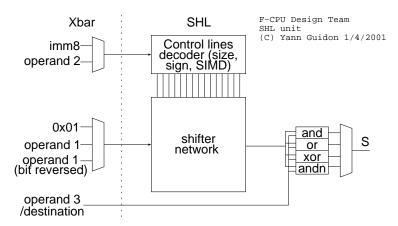

| 3.1 | Detail of the ROP2 unit                                                           |

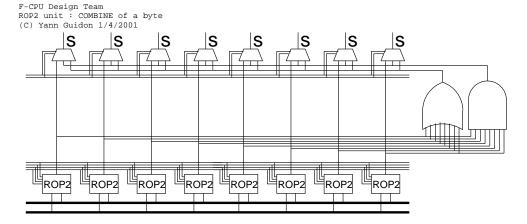

| 3.2 | Description of the COMBINE function on top of ROP2 for a byte-wide SIMD packet 53 |

| 3.3 | Overview of the Scrambling unit                                                   |

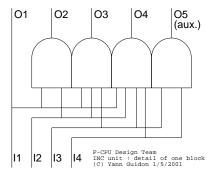

| 3.4 | Description of one block of the AND tree                                          |

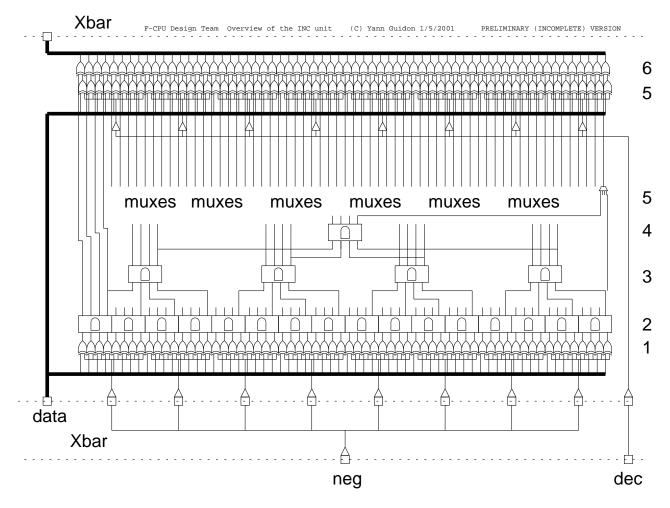

| 3.5 | Overview of the Incrementer Unit (preliminary version)                            |

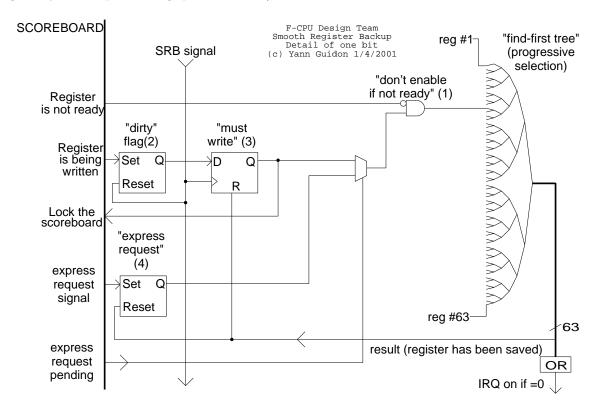

| 2.1 | Detail of one bit of the SRB flags and decision mechanism                         |

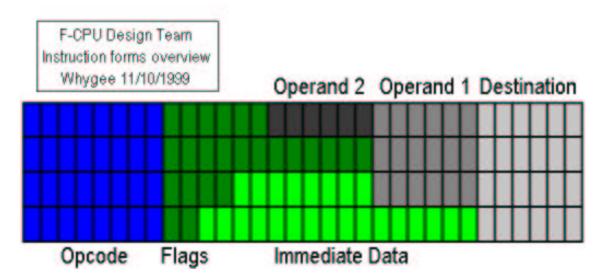

| 1.1 | Preliminary overview of the instruction forms                                     |

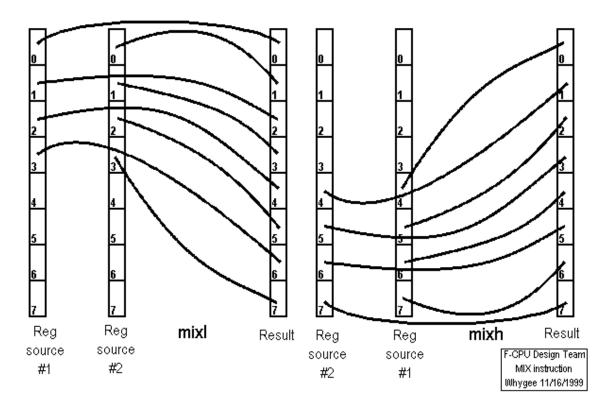

| 2.1 | Description of the mix instruction                                                |

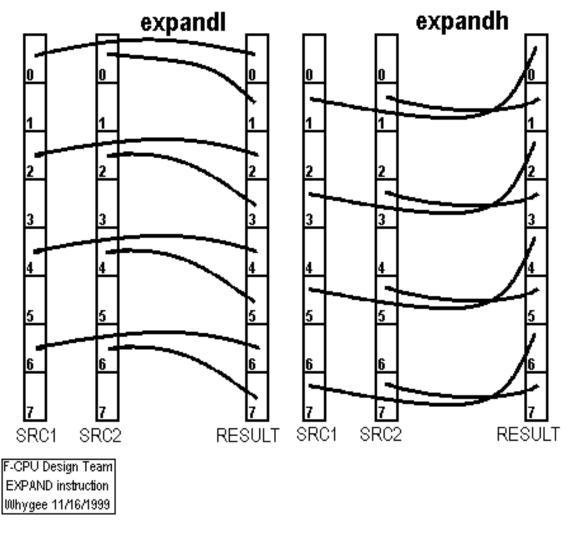

| 2.2 | Description of the expand instruction                                             |

## List of Tables

## Part I

## The F-CPU Project, description and philosophy

## Chapter 1

## Description of the F-CPU project

There is no exact definition of the F-CPU project. It is not possible because of the amount of history, discussions, details that forge the specificity of this undertaking. We can however highlight some important facts and points.

The F-CPU architecture defines a SIMD, superpipelined, 64-bit RISC microprocessor. As of today, it is the only CPU of this kind which can be completely parameterized: it is not bound to 64-bit implementations and it is intended to scale up easily. Furthermore, it is the only processor of this class that is available with all the (VHDL) source code and manuals distributed with the GNU licence (GPL and GFDL). It is meant to be a totally ununcumbered design targeted at the widest range of technologies as possible.

The F-CPU project is also formed by a lot of people, discussing on mailing lists about the organisational and technical sides of the design. The mailing lists are public places where the processor is transparently designed with contradictory discussions. Everybody can come and influence the specifications if the modification respects the design and the project's goals.

The F-CPU group is one of the many projects that try to follow the example shown by the GNU/Linux project, which proved that non-commercial products can surpass expensive and proprietary products. The F-CPU group tries to apply this "recipe" to the Hardware and Computer Design world, starting with the "holy grail" of any computer architect: the microprocessor.

This utopic project was only a dream at the beginning but after two group splits and much efforts, we have come to a rather stable ground for a really scalable and clean architecture without sacrificing the performance. Let's hope that the third attempt is the good one and that a prototype will be created anytime soon.

The F-CPU project can be split into several (approximative and not exhaustive) parts or layers that provide compatibility and interoperability throughout the whole project's lifespan (from HardWare to SoftWare):

- \* F-CPU Peripherals and Interfaces: bus, chipset, bridges...

- \* F-CPU Core Implementations: individual chips, or revisions (for example, F1, F2, F3...)

- \* F-CPU Cores generations, or families (for example, FC0, FC1, etc.)

- \* F-CPU Instruction Set and User-visible ressources

- \* F-CPU Application Binary Interface

- \* Operating System (aimed at Linux-likes)

- \* Drivers

- \* End-User Applications

Any layer depends directly or indirectly from any other. The most important part is the Instruction Set Architecture, because it can't be changed at will and it is not a material part that can evolve when the technology/cost ratio changes. On the other hand, the hardware must provide binary compatibility but the constraints are less important. That is why the instructions should run on a wide range of processor microarchitectures, or "CPU cores" that can be changed or swapped when the budget changes.

Any core family will be binary compatible with each other and execute the same applications, run under the same operating systems and deliver the same results with different instruction scheduling rules, special registers, prices and performances. Each core family can be implemented in several "flavours" like

a different number of instructions executed by cycle, different memory sizes, different word sizes, but the software should directly benefit from these features without (much) changes.

This document is a study and working basis for the definition of the F-CPU architecture, aimed at prototyping and first commercial chip generation (codenamed "F1"). This document explains the architectural and technical backgrounds that led to the current state of the "FC0" core as to reduce the amount of basic discussions on the mailing list and introduce the newcomers (or those who come back from vacations) to the most recent concepts that have been discussed.

This manual describes the F-CPU family through its first implementation and core. The FC0 core is not exclusive to the F-CPU project, which can and will use other cores as the project grows and mutates. The FC0 core can also be used for almost any similar RISC architecture with some adaptations.

The document will (hopefully) evolve rapidly and incorporate more and more advanced discussions and techniques. This is not a definitive manual, it is open to any modification that the mailing list agrees to make. It is not exhaustive either, and may lag as the personal free time fluctuates. You are very encouraged to contribute to the discussion, because nobody will do it for you.

#### Some development rules:

- \* This Project is an experiment to prove it's possible to develop a processor in a bazaar-style environment. The decisions are made by discussion and consensus on the mailing list.

- \* There is no leading or ivory tower (this is not a "cathedral"). In fact this is a "Crtistal tower" because everything is as transparent as possible. Anyone may join the team and contribute or even contribute without officially "joining" in any way. Even those with limited or no knowledge of CPU development can have something to contribute. A lot of motivation and free time is required, however ...

- \* The name of the game is Freedom, so our designs are being developed openly and will be openly distributed under the GNU Public License, so anyone will be able to (if they have the funding at least) use our designs, manufacture and sell their own F-CPU or derivative chips, but any changes will have to be made freely available again. Read the GNU Public Licence and the F-CPU charter for more details.

- \* We are aware of the extreme ambitiousness of this Project, but we believe it to be necessary for the continued existence of free software in a world of increasingly proprietary hardware, so we will persevere until we are successful.

- \* We are also fed up of being forced to use proprietary HW because we are not able to influence the platform. As users, we understand that Free Software can't blossom without Free Hardware.

- \* Remember, here at the Freedom CPU Project we are not anti-Intel, anti-Microsoft, or in fact anti-anything. We are only pro-Freedom!

- \* Never flame, never respond to flame bait, but please do make and take constructive criticism.

- \* "Design and let design" could sum up most of the behaviours adopted in the group. Some strong disagreements have and will appear during the discussions, but whether the subject correspond to the f-cpu goals or not, everybody has the right to play with his ideas. Do not force others to agree, but discuss constructively and explore the subject, instead of flaming other's idea down. A good architecture can come from a mutual respect, not from flame wars.

## Chapter 2

## Frequently Asked Questions

Collected from different sources. Last modified by Whygee, jan, 14 2000

#### 2.1 Introduction

Q1: What is the F-CPU?

A: The F-CPU is a inherently SIMD, 64-bit, superpipelined microprocessor, available with VHDL source code and distributed under the terms of the GNU Public Licence. It is being developed by a community of hobbyists, students and professionals on the Internet.

$\underline{\rm Q2}$  : Why a 64-bit RISC CPU ? I want to make a x86 clone / a soundcard / a 32-bit embedded core ...

A: http://www.opencollector.org

The original goal of a high performance 64-bit CPU dates back to the early days of the project when the founders wanted to counter the Merced (ia64). If you desire something else, there is a great chance that a project already exists with a goal similar to your requirements. The OpenCollector is one of the websites that list the "free" projects that you can access on the Internet. If you don't find what you want, don't hesitate to create your own project.

There are already a lot of free CPU projects available on the Internet. If you desire a 32-bit-only CPU, the MIPS/DLX and the LEON CPUs are good starting points, even though the F-CPU can be easily scaled down to 32 bits. If you require a 16-bit or 8-bit microcontroller, there are also a lot of free (in different ways) designs. You just have to pick one from the lists of the OpenCollector website. If you are sure that you want a F-CPU-like processor, be sure to read and understand this manual before you go further in your project. The goals of the project are firm and will not change because of an individual's whim.

#### 2.2 Philosophy

Q1: What does the F in F-CPU stand for?

A: It stands for Freedom, which is the original name of the architecture, or Free, in the GNU/GPL sense.

The F does not stand for free in a monetary sense. "Free" doesn't mean "free as free beer" but "freely copiable and modifiable". You will have to pay for the chip, just as you have to pay nowadays for a copy of a GNU/Linux distribution on CD-ROMs. Of course, you're free to take the design and masks to your favorite fab and have a few batches manufactured for your own use.

#### Q2: Why not call it an O-CPU (where O stands for Open)?

A: There are some fundamental philosophical differences between the Open Source movement and the original Free Software movement. We abide by the latter, hence the F.

The fact that a piece of code is labeled Open Source doesn't mean that your freedom to use it, understand it and improve upon it is guaranteed. Further discussion of these matters can be found at htpp://www.gnu.org.

We tried to make a licence similar to the GPL (GNU Public Licence from the Free Software Foundation) (see http://www.opencollector.org/hardlicense/) but this effort has been abandonned because it doesn't seem necessary or useful. Today it is replaced by an external charter that strengthens the meaning of the GPL.

Specifically, there are at least three levels of freedom that must be preserved at any cost:

- Freedom to use the Intellectual Property: no restriction must exist to use the work of the F-CPU project. This means, no fee to access the data and ALL the necessary informations to recreate a chip.

- Freedom to reverse-engineer, understand and modify the Intellectual Property at will.

- Freedom to redistribute the design files.

This design is NOT public domain. The F-CPU group owns the IP that it produces. It chooses to make it freely available to anybody by any means. Every file or hardware generated from the description files and the Intellectual Property of the F-CPU team keeps the copyright of the F-CPU team. You can read more about it at http://www.gnu.org.

#### Q3: How is the F-CPU design protected?

A: The F-CPU Design Team protects his work with the copyright laws. Every file holds the copyright notice and the GPL notice. Nothing else is required.

Additional measures should ensure that no patent issue will arise in the future. Patents are well known for their inefficiency and high cost. The F-CPU design team is protected because it only describes the device, while issues appear when the design is implemented. We must publish proofs of prior art, during conferences and in the press, to avoid the remaining troubles. In the end, the design must remain totally unencumbered.

#### Q4: And what if I patent a feature of the F-CPU?

A: You will loose time and money, that's all.

First, the design is based on common techniques that are heavily studied for thirty years. You'll have a hard time explaining what is new enough to justify a patent.

Second, if the patent is accepted, noone will accept to pay the royalties on something that was stolen from the F-CPU team. Suing the implementors will lead to nothing and in the end, you will own a useless patent that gives you only worries.

#### Q5: Why would my company use the F-CPU instead of another core?

A : The technical advantages of the F-CPU are described in this manual : extreme scalability and orthogonality, ununcumbered and clean design, emphasis on performance, simplicity and retargetability to various technologies (FPGA/ASIC...)

However the non-technical side of the project might ring a bell if you want to integrate the F-CPU core in your design. The design files are available at no charge, but it's not the only meaning of the "free" in the F-CPU. It is a transparent design, it is not a "black box" obfuscated by a proprietary and closed team. If you're in troubles, (for example: the design is deprecated, abandonned by the company or it runs out of business, in short: you're left alone with the design) you don't have to reverse-engineer the "black box" to figure out what goes wrong. You simply read the source code and patch it. The F-CPU is distributed under the terms of the GPL which gives you all the rights to understand and modify (customize) the files.

Another aspect concerns the legal expenses. Just as the GPL is called a "gentleman agreement", the F-CPU is a "gentleman's CPU". We promote peaceful collaboration between the teams: more budget can be dedicated to research and design, less money is spent for the legal departments. In the end, everybody wins because the teams can be larger and spend all their time on the quality of the design and the time to market, rather than on expensive endless lawsuits. "Design and let design": the only interesting and determining things are the reaction time and the efficiency (cost, performance, ease of use) of the product.

#### Q6: Great but what are the fine lines? Are there drawbacks?

A: They are contained in the GPL and the F-CPU charter. Just as the design was brought to you free, you have to keep it free and redistribute all the modifications or additions to the core. Because the F-CPU (like all GPL projects) is based on collaboration/cooperation and not competition, your enhancements will benefit others but they can also enhance on your enhancements and this will benefit you in return.

If you want to keep your design secret, don't integrate the F-CPU in your project. You will not be able to benefit from other's work and experience. You will have to reinvent the wheel and loose time and money.

#### 2.3 Tools

#### Q1: Which EDA tools will you use?

A: There has been a lot of debate on this subject. It's mainly a war between Verilog and VHDL. We have started with VHDL'93 for convencience because it is most used in Europe (where most of the code is written) but it will certainly be translated to other file formats. Currently, the design exists in VHDL'93 only for convenience and uniformity. The other representations will be derived from it.

Now that VHDL is the main langage, VHDL tool choices are more limited. We want to promote GNU EDA SW but this branch is not yet developed or mature enough. A particular software may be difficult to install, another may be unstable, outdated or not compliant with today's standards and requirements.

The use of Alliance (http://www-asim.lip6.fr/alliance/) is considered but it will be useful only during the layout process. Other free tools and designs can be found from http://www.opencollector.org.

Today we use Simili (http://www.symphonyeda.com) under the Win32 platform. It is not a GNU software but has many advantages such as independence, compliance with the IEEE standard, ease of use, compacity... We expect a Unix port in the future, as well as other good GNU EDA software.

The sources have also been compiled without modification with FreeHDL and Modelsim. Other IEEE compliant compilers will certainly confirm the high portability and quality of the design.

Cadence has just proposed free licences for some of its tools. Other offers will probably follow and are welcome, as long as the "counterparts" are compatible with the F-CPU charter.

We'll probably use commercial products at one point or another because the chip makers use proprietary software. In any case, a pen, paper and a brain always help.

#### 2.4 Architecture

Q1: What's that memory-to-memory architecture I heard about? Or this TTA engine? Why not a register-to-register architecture like all other RISC processors?

A: M2M was an idea that was discussed at the beginning of the F-CPU project. It had several believed advantages over register-to-register architectures, like very low context switching latency (no registers to save and restore). Today, the SRB mechanism included in the FC0 solves this problem (see the Part IV, chapter 3, "The Smooth Register Backup mechanism").

TTA is another architecture that was explored before the current design (FC0) started.

The F-CPU architecture might evolve in the future and borrow some new features of other architectures.

#### Q2: You're thinking about an external FPU?

A: No. Bandwidth and pin count problems. We can easily fit such units on a chip today.

#### Q3: Why don't you support SMP?

A: Symmetric Multi-Processing like it is implemented on low-end PCs limits the performance and scalability of the architecture. We're actively investigating other architectures, mainly Non-Uniform Memory Access through a specific bus called F-BUS. We try to avoid all the complex techniques needed by multi-CPU processing. No firm decision has been made as of today. The F-CPU core is independent from the bus interface anyway, almost any type of connexion can be implemented.

#### 2.5 Performance

#### Q1: What can we expect in terms of performance from the F1 CPU?

A: Merced-killer.:-). No seriously, we hope to get some serious performance, though it would be impossible to make any claim before we can measure the performance of a real chip.

We think we can achieve good performance because we start from scratch (x86 is slower because it has to be compatible with older models).

LINUX and GCC are not the best garanties for performance in themselves. For example, GCC doesn't handle SIMD data. We will certainly create a compiler that is more adapted to the F-CPU and GCC will be used as a "bootstrap" for the "legacy SW" at the beginning. The ongoing work on GNL and XML-based interfaces will probably allow developpers to create better code than what GCC would ever do.

Objectively, the FC0 core family is aimed to achieve the best MOPS/MIPS ratio possible, around 1 (and maybe a bit more). The superpipeline garanties that the best clock frequency is reached for any silicon technology. The memory bandwidth can be virtually increased with different hint strategies. So we can predict that a 100MHz chip with 1 instruction decoded at each cycle can easily achieve 100 million operations per second. Which is not bad at all because you can achieve that with an "older" (cheap) silicon technology that couldn't achieve 100MOPS with a x86 architecture. Add to that the unconstrained SIMD data width, and you get a picture of the peak MOPS it can reach. If you really want screaming numbers, with a 64-bit version, SIMD operations on bytes leads to 8 operations per cycle, or 800MOPS peak.

#### 2.6 Compatibility

#### Q1: Will the F-CPU be compatible with x86?

A: No. Nada. Niet. Nein. Non.

There will be NO binary compatibility between the F-CPU and x86 processors. It could however run Windows emulators that include x86 CPU emulators such as Twin, as well as Windows itself under whole-PC emulators such as Bochs. In either case however you will need to run another operating system, such as GNU/Linux, and emulation will likely be fairly slow. But what would be the point of using Windblows when you can run GNU-Linux/xBSD instead?;-D

## Q2: Will I be able to plug the F-CPU in a standard Socket 7, Super 7, Slot 1, Slot 2, Slot A or any other existing motherboard?

A: Great chances are that no version of the F-CPU will ever be available for Socket7 or any x86 mother boards.

Reason 1: the BIOS should be rewritten, the chipsets should be analysed, and there are way too many chipsets/motherboards combinations around. It is clearly out of the scope of our project.

Reason 2: Socket/pins/bandwidth: the x86 chips are really "memory bound", the bandwidth is too low, some pins are not useful for a non-x86 chip, and supporting all the functions of the x86 interface will make the chip (its design and debugging) too complex, more expensive and slower.

Reason 3: we don't want to pay the fees for the use of proprietary slots.

ALPHA- or MIPS-like slots will probably be supported, we might include an EV-4 interface to the F-CPU standard. Anyway, a custom socket and interface will avoid any compatibility and misunderstanding problem. If you want to plug your F-CPU chip on something else, "just do it".

#### Q3: What OS kernels will the F-CPU support?

A: Linux will probably be ported first. Other ports will follow and different kernel types are possible. But first we must have a working software development tool for the architecture, thus we must first fully define the F-CPU ...

#### Q4: What programs will I be able to run on the F-CPU?

A: We have a first prototype/preliminary port of gcc/egcs for the Freedom architecture. Basically the F-CPU will run all the software available for a standard GNU/Linux distribution, except the low-level parts such as assembly, I/O and bootstrap code.

Remember that GCC is not perfectly adapted to fifth generation CPUs. We have adapted it for the F-CPU but it was very difficult and it supports only a small subset of the capabilities of the F-CPU ISA. Don't expect good performance from the generated code, at least for the FC0.

#### 2.7 Cost/Price/Purchasing

#### Q1: Will I be able to buy a F-CPU someday?

A: We hope so. That's all the point of the project, but be patient and take part of the discussions! If you think it is not developed fast enough, join the team and help us. Before the F-CPU will exist in a chip, it will be available in other forms such as software or hardware emulations or simulations.

#### Q2: How much will the F-CPU cost?

A: We don't know. It depends on how many are made. There was an early slightly optimistic estimate that an F-CPU would cost approximately \$100, if 10000 were made. This also depends on a lot of factors like the desired performance, the size of the cache memory, the number of pins, and most of all, the possibility to combine all these factors in the available technology. The latest estimations for a first limited version gave around \$60 each for a batch of 1K ASIC. The FC0 chip looks a bigger and simplified 486, it belongs to the class of 1 million transistors chips. It is more than the LEON core or the ARM, but it is small compared to other 64 bit chips. Therefore it shouldn't be as expensive as a high-end CPU.

## Chapter 3

## The genesis of the F-CPU Project

A lot of things have happened since the following document was written. The motivation has not changed though, and the method is still the same. The original authors are unreachable now but we have kept on working more and more seriously on the project. At the time of writing, several questions asked in the following text have been answered, but now that the group is structuring itself, the other questions become more important because we really have to face them: it's not utopy anymore, the fiction slowly becomes reality.

Don't forget too that the technical features that are described here are NOT realistic and don't correspond to anything real. This was more a dream than a coherent analysis. Please don't flame us for other's dreams.

#### 3.1 The Freedom CPU Architecture: A GNU/GPL'ed highperformance 64-bit microprocessor developed in an open, Web-wide collaborative environment.

Authors: Andrew D. Balsa w/ many contributions from Rafael Reilova and Richard Gooch.

5 August 1998

#### 3.1.1 History

The idea of a GNU/GPL'ed CPU design sprang in the middle of some email exchanges between three long-time GNU/Linux users (also Linux kernel developers in their spare time) with diverse backgrounds.

We were questioning monopolies and how the dominance of an operating system (including the kernel, the Graphical User Interface and the availability of "killer-applications" as well as documentation) was intimately related to the world-wide dominance of a specific, outdated, awkward and inefficient CPU architecture. I guess we all know what I am referring to.

We also expressed our faith that GNU/Linux is well on its way to provide the basic foundation for a totally Free software environment (in the GNU/GPL sense; please get a copy of the GNU GPL license if you are reading this, or check www.gnu.org). However, this Freedom is limited or rather bound by the proprietary hardware on which it feels most at home to run: the traditional x86-based PC.

Finally, we were worried that Intel's attitude of not releasing advance information to the Free Software community about its forthcoming Merced architecture would delay the development of a compatible gcc compiler, of a custom version of the Linux kernel, and finally of the vast universe of Free Software tools. It is vaguely rumoured that Linus Torvalds may have received advance information on Merced by signing an Intel NDA, but this would be an individual exception and wouldn't really fit with the spirit of Free Software. On the whole, even though Merced will certainly be more modern that the x86 architecture, it will be a step backwards in terms of Freedom, since unlike for the x86, there will most likely never be a Merced clone chip.

In the previous days, we had been discussing the various models for Free Software development, their advantages and disadvantages. Putting these two discussions together, I quickly drafted an idea and posted it to Rafael and Richard, warning them that this would be good reading while they were compiling XFree86 or a similarly large package... and then they liked it! Here is this crazy, utopic idea, merged with comments, criticism and further ideas from Rafael and Richard:

#### 3.1.2 The Freedom GNU/GPL'ed architecture

We started with some questions:

- Why don't we develop a 64-bit CPU and put the design under the GNU General Public License?

- Why don't we make the development process of this new CPU completely open and transparent, so that the best brains worldwide can contribute with the best ideas (somehow using the same communication mechanisms traditionally used by the Free Software community)?

- How can we make the CPU development process entirely democratic and truly open, whereas it is usually surrounded by paranoia and secrets?

- How can we design something that will improve in \*technical\* \*grounds\* on what will be available in 2000 from the most advanced CPU architecture team ever put together by any corporation (the Merced)?

There are really two distinct incredible challenges here:

- a) the performance and feasability of the resulting architecture, and

- b) the open development process under a GNU/GPL license and the intellectual property rights questions raised by this process.

Tackling a) first (performance and feasability), we think the Freedom architecture could be more efficient under GNU/Linux compared to other architectures by making it:

- 1. More compatible with the gcc compiler. We have the source code to gcc, but most importantly, we have the gcc developers available to help us figure out what features they would like to see in a CPU architecture. Why gcc? Because it is the cornerstone of the entire body of Free Software. Basically, an efficient architecture for gcc will see an increase in efficiency across-the-board on \*all\* Free Software programs.

- 2. Faster in the Linux kernel. Right now, if we take for example the PC architecture, we notice that the Linux kernel has to "work around" (and some would say "work against") various idiosyncrasies of the x86/PC specifications and hardware. We also have to maintain compatibility with outdated x86 chips. And obviously, there is no possibility of implementing some of the often used Linux kernel functions in silicon. A new design, custom fitted to the Linux kernel code, would vastly improve the performance of any kernel-bound applications.

Further ideas for a possible architecture and implementation can be found in the appendices (as well as the "economics" of the project). Note that we are calling the architecture "Freedom" (for obvious reasons), and its first implementation "F1". Projected end-user cost of an F1 CPU is around \$100. Everything is very utopic, we know. : -)

However, it also seems to us that at this stage, the real challenges for our project are entirely within b): the development process and the intellectual property issues.

#### 3.1.3 Developing the Freedom architecture: issues and challenges

The Dilbert cartoon says it all, in fact: our project \*is\* a whole new paradigm! What we are basically proposing is to bring together the competences and creative powers of thousands of individuals over the Web into the design process of an advanced, Free, GNU/GPL'ed 64-bit CPU architecture. And we don't even know if it's possible!

We know two things for sure:

• In the past and present, corporations like Intel, IBM and Motorola are known for having broken down design teams, so that no close groups could be formed that would be able to recreate the entire design (and eventually quit and form their own companies). Recently, Andy Grove has given a new meaning to the word "paranoia" as a management tool. Our proposed Free, open, transparent, collaborative environment counters this trend. It is also in a large part related to some new trends in Human Resources management and Organizational theory. In fact, it is very akin to the concept of Virtual Corporations, except that in this case we are rather dealing with a Virtual Non-Profit Organization. In this respect, the Freedom project is also an experiment in Organizational theory, but it's not a gratuitous experiment. Many studies indicate that keeping people in small closed groups, bound by strict NDA and other legal constraints to public silence, and putting a relatively high amount of pressure on these groups, is not the best method to unleash creative powers. It also sometimes leads to buggy designs...

- The development of the Linux kernel, by a group of highly talented programmers/system developers is an example that an open, collaborative environment aiming for a GNU/GPL'ed piece of software with a particularly high intellectual/technological value, is possible. Moreover, it can be shown that in some areas, the Linux kernel performs better then its commercial counterparts. However, this list of certainties is rather short compared to the list of questions generated by our proposal:

- How will new ideas be selected or discarded for inclusion in the design, amid the inevitable "noise" of Bad Ideas (tm)? Who will be the judge of what's Good and Bad?

- Also inevitably, mutually exclusive options/features will appear during the course of development. Again, who will decide on the direction to be chosen?

- Who will own the final design intellectual property rights? Is the "copyleft" applicable in the case of a CPU design? What about the masks for the first silicon?

- Will the GPL be sufficient as a legal instrument to protect the design? What changes, if any, will have to be made to the GNU/GPL to adapt it to a chip design?

- If the design process uses commercial EDA and other tools, in what measure do these proprietary items "taint" our GNU/GPL'ed design? Is it possible to separate the GPL part from the commercial/proprietary parts?

- What about existing patents? Will the project need any? Will it be able to "buy" any, or pay royalties?

- Contrarily to a piece of software, partial implementations of the Freedom design will not be possible. The first implementation that will go to silicon \*must\* be functional and complete. All "holes" in the design must be plugged before the first mask gets drawn. How do we make volunteers accept such a rigid schedule?

There are some questions raised as a consequence of the possible succes of the Freedom implementation:

- There are vast possibilities for a GNU/GPL'ed CPU design in the industrial, medical, aeronautical, automotive and other domains. In fact, a Free, stable, high-performance design offers possibilities never before envisioned by hardware designers in various domains. Is this the beginning of a small revolution in e.g. embedded hardware?

- Will the design sustain itself over the years as the ideal GNU/Linux processor?

- Can this experiment in open development have other consequences on the electronics industry? Are we really proposing a new paradigm for CPU development? Can this paradigm be applied to other VLSI designs?

#### 3.1.4 Tools

We all know the saying: "If the only tool one has is a hammer...". We'll need "groupware" tools for the Freedom project, but the word "groupware" has a bad reputation nowadays. We prefer to use "collaborative work tools". Some of them have only come into existence and widespread use in the last decade; I am obviously talking about the Web itself, and its assortment of communication technologies: email, newsgroups, mailing lists, Web sites, SGML/PDF/HTML documentation and editing/translation software. Much of this infrastructure is/has been used to develop GNU/Linux, and is nowadays based on GNU/Linux, BTW.

But we'll also need new tools, that perhaps don't even exist yet. I think it's worth mentionning that perhaps one the greatest steps in this direction is the WELD project, developed at Berkeley. It could well become the cornerstone of the Freedom project, or conversely, the Freedom project can perhaps be thought of as the ideal, perfect test case for the WELD project.

#### 3.1.5 Conclusion

The conclusion is simple and obvious:

- if you are a CPU architect/VLSI engineer, or

- if you have a good idea on CPU design that you have been toying with for some time and would like to test, or

- if you just like challenging intellectual propositions and brainstorming interaction :

Please join and help us turn this idea into a reality!

\* : Richard is an Australian astrophysicist preparing his Ph.D. on astronomic visualization; Rafael is a researcher on EDA tools at the University of Cincinatti. I am an ex-Ph.D. student in Management and an ex-firmware engineer, with a special interest in Ethical problems in multi-cultural environments (I was born in Brazil and am presently living in France). None of us has any formal education in CPU architecture. Rafael comes closest, since he is in VLSI design and EDA tools development, and also developed some new code for CPU recognition in the Linux kernel. Richard developed the Pentium Pro MTRR support in the Linux 2.1.x kernels (as well as other novel kernel routines), and is also a hardware developer. I have the honour of having diagnosed the Cyrix 6x86 "Coma" bug and proposed a workaround for it under GNU/Linux (both were at first rejected by Cyrix Corp.). I am also a long time hardware and firmware developer, and have contributed in various ways to GNU/Linux development (e.g. the Linux Benchmarking HOWTO).

Richard E. Gooch < Richard. Gooch@atnf.csiro.au >

Rafael R. Reilova < rreilova@ececs.uc.edu>

Andrew D. Balsa <andrebalsa@altern.org>

note: today, none of these addresses work. altern.org has even disapeared.

#### 3.1.6 Appendix A

#### Ideas for a GPL'ed 64-bit high performance processor design

This is just a dream, a utopic idea of a free processor design. It's also a list of things I would like to see in a future processor.

- This project will need a sponsor if it ever wants to become a reality. Getting first silicon is not going to be free, nor easy.

- Choice of a 64-bit datapath, address space: obvious nowadays. Simplifies just about everything.

- Huffman encoded instruction set: improves cache/memory—CPU bandwidth, which is one of the main bottlenecks nowadays. Should be quite simple to add a Huffman encoder to a compiler back-end. All instructions lengths are multiple of byte.

- RISC vs. CISC vs. dataflow debate: it's over! Get the advantages of each, disadvantages of none as much as feasible.

- 1, 2 or 4 internal 7-stage pipelines.

- Speculative execution : 4 branches, 8 instructions deep each.

- 64-byte instruction prefetch queue.

- 32-byte write buffers.

- Microprogram partly in RAM. Must be able to emulate x86 instruction set (assembler source level).

- 64-bit TSC w/ multiple interrupt capabilities.

- Power saving features.

- MMX and 3DNow! emulation.

- Fully-static design (clock-stoppable).

- F1 implementation: 128 bits external data path, 40 bits external addressing capabilities.

- Performance monitoring registers "a la" Pentium.

- External FPU, memory mapped (have no idea what it should look like). FPUs can be added to work in parallel (up to 4?). Separate bus. Same bus can handle a graphics coprocessor with its dual-ported memory.

- 8KB 4-ported L1 unified cache, with independent line-locking/line-flushing capabilities. Can be thought of as a 1 KB register set.

- Separate 64KB each L2 instruction and data caches, running at CPU speed.

- Integrated intelligent DMA controller, 32 channels.

- Integrated interrupt controller: 30 maskable interrupts, 1 System Management interrupt, 1 non-maskable interrupt.

- 0 internal registers! Yep, this is a memory-memory machine. Instruction set recognizes 32 pseudoregisters at any moment.

- Interrupts cause automatic register set switch to vectored register set : 0 (zero) context switch latency!

- No penalty for instructions that access byte, word, dword data.

- Operation in little or big-endian mode "a la" MIPS.

- Paging "a la" Intel, with 4k pages + 4M extension.

- Also VSPM "a la" Cyrix 6x86, with 1K definable pages.

- ARR registers "a la" Cyrix 6x86 (similar to MTRR on Intel PPro): allows defining non-cacheable regions (useful for NUMA, see below).

- Internal PLL with software programmable multiplier; can switch from 1x to 2x to 3x to nx in 0.5 increments, on-the-fly.

- The MMU should also support object protection "a la" Apple Newton.

- Single-bit ECC throughout.

- Direct support of 4 1MB dual ported memory regions for NUMA-style multiprocessing (also on FPU bus).

- CPU architecture project name: "Freedom". Could also be called "Merced-killer", or "Anti-Merced", or "!Merced", but in fact we are not anti-anything with this project. We are just pro-Freedom and open; what we dislike about the Intel Merced is its proprietary design and restrictive development environment. I guess the challenge here is to determine whether a GPL'ed CPU design is feasible. Is open, collaborative development possible WRT CPU design? How does one get the funding to actually put the design on silicon, once it is ready? How can revisions be handled? Are there patents that would inherently block such a development process?

The idea also is to use gcc as the ideal development compiler for this CPU (unlike Merced). And to be able to port the Linux kernel with a minimal effort on this new processor.

#### 3.1.7 Appendix B

#### Freedom-F1 die area / cost / packaging physical characteristics / external bus

Just as a reminder, the F1 CPU does not include an FPU or 3DNow! unit (but SIMD integer instructions will be included).

Recommended maximum size: 122 sq. mm. This gives us 200 dies/8-inch wafer (see an example of such a wafer on Hennessy and Patterson, page 11).

Roughly, die yield = 0.5 for our 122 mm2 5-layer 0.25 micron CPU (H AND P, page 13, updated to reflect better fabs). This allows more or less 10-11 million transistors, divided as follows: 6-7 million for the caches, 4-5 million for the rest.

Assume wafer yield = 95, final test yield = 95. Testing costs of \$500/hour, 20 seconds/CPU.

Packaging costs = \$25-50 (see below).

Roughly, following H and P, this gives us a unit cost of \$75-100/good CPU, tested, boxed in antistatic packaging and shipped to the US, if the Taiwan foundries can keep the wafer processing cost around \$3.500.

Packaging: I am going to propose something surprising, but I think we should use the same packaging as the Celeron CPU, in terms of physical dimensions and CPU placement. Like that we can also use the Celeron heatsink/fans already in the market, and the Celeron mounting hardware.

PCI set: again I am going to propose a heresy, but I think we could use 100MHz Slot 1 motherboards. First, Intel is not alone anymore manufacturing Slot 1 chipsets: VIA has just released a Slot 1 chipset with excellent performance and the latest goodies in terms of technology (we can get timing info from the VIA chipset datasheets). Second, we don't have to worry about the motherboard/PCI set issue anymore. Third, it's almost impossible to go beyond 100MHz on a standard motherboard, because of RFI issues; so basically 100-112MHz is as good as it gets. Fourth, there will be many people out there with Slot 1 motherboards, willing to upgrade their PII/Celeron CPUs (specially the Celeron). Fifth, these motherboards are nowadays quite cheap, and we get all the benefits of high-volume production. Sixth, this allows easy upgrades of the Freedom CPU to higher speed grades, larger cache versions, FPU-with versions, etc.

Now, if we accept the above, we have to put on the Celeron-style Freedom printed circuit a small EEProm that will contain the Freedom BIOS, the L2 cache and a socket for the FPU. This increases the cost of the CPU, but decreases overall costs, so I still think it's a good move.

Please check a photograph of the Celeron and tell me if I am just dreaming.

#### 3.1.8 Appendix C

#### Legal issues / financial issues

August 5, 1998

We would like to have support from the Free Software Foundation for the Freedom project.

We are not proposing that the Free Software Foundation build a fab. What we are saying is: if we go to a foundry in the US or Taiwan, give them a mask, and ask them to run a batch of 0.25 micron, 5 layer 8-inch wafers for us, they'll quote approx. \$3K-5K or less even, per wafer, as their price (our cost) for our batch (in the year 2000).

An approximate cost for a batch of F1 CPUs would theoretically be somewhere between \$500k and \$1000K, for 5000-10000 good CPUs.

Not exactly pocket money, but we could sell those CPUs on a subscription basis. Like this: people who would subscribe would get the Merced-killer for around \$100 (compare that to the projected cost of \$5000/unit for the Merced), on a first-come/first served basis, and any left-over CPUs after the cost of the batch would be covered, could be sold for a slightly higher price to pay for the next batch and further mask development.

We suggest putting some quotas in the system. Demand is likely to be higher than supply. ;-)

The Free Software Foundation could coordinate all the legal/financial/logistic aspects of the project (and would be adequately compensated for this work). This, of course, would depend on getting support from Mr. Stallman for this initiative.

## Chapter 4

## A bit of F-CPU history

(And a reflexion on the evolution of the F-CPU through a description of the different proposed architectures)

#### 4.1 M2M

The first generation was a "memory to memory" (M2M) architecture that disapeared with the original F-CPU team members (they have written the previous text). It was believed that context switch time consumed much time, so they mapped memory regions to the register set, as to switch the registers by changing the base register. I have not tracked down the reasons why this has been abandonned, I came later in the group. Anyway, they launched the F-CPU project, with the goals that we now know, and the dream to create a "Merced Killer". Actually, i believe that we should compete with the ALPHA directly;-)

#### 4.2 TTA

The second generation was a "Transfer Triggered Architecture" (TTA) where the computations are triggered by transfers between the different execution units. The instructions mainly consist of the source and destination "register" numbers, which can also be the input or output ports of the execution units. As soon as the needed input ports are written to, the operation is performed and the result is readable on the output port. This architecture has been promoted by the anonymous AlphaRISC, now known as AlphaGhost. He has done a lot of work on it but he has left the list and the group lost track of the project without him.

Brian Fuhs (bkfuhs1@attglobal.net) explained TTA on the mailing list this way :

TTA stands for Transfer-Triggered Architecture. The basic idea is that you don't tell the CPU what to do with your data, you tell it where to put it. Then, by putting your data in the right places, you magically end up with new data in other places that consists of some operation performed on your old data. Whereas in a traditional OTA (operation-triggered architecture) machine, you might say "ADD R3, R1, R2", in a TTA you would say "MOV R1, add; MOV R2, add; MOV add, R3". The focus of the instruction set (if you can call it that, since a TTA would only have one instruction: MOV) is on the data itself, as opposed to the operations you are performing on that data. You specify only addresses, then map addresses to functions like ADD or DIV.